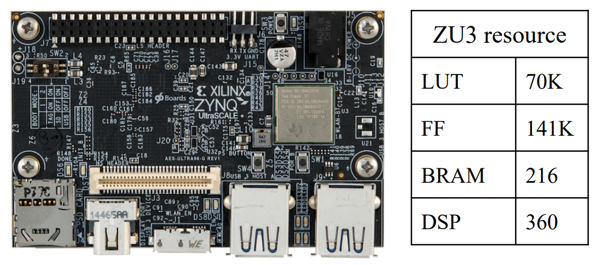

DAC SDC(System Design Contest)的比赛任务是在Xilinx Ultra96v2平台上实现高速、高准确率且低功耗的飞行器高空目标检测深度学习算法。比赛所用的训练与测试数据集均由大疆公司提供,训练集包含95种目标共93K张图片,测试集包含52K张图片,最终将以检测精度(IoU)高、速度(FPS)快和功耗低为评判准则。

前言

读研期间,主要研究面向目标检测领域的加速器设计,包含两个项目:一个是2021 DAC System Design Contest 低功耗单目标检测系统设计竞赛,另一个是面向自动驾驶多目标检测场景的可配置深度学习加速器设计。这篇文章主要介绍一下2021 DAC System Design Contest 低功耗单目标检测系统设计竞赛。

项目介绍

任务介绍

DAC SDC(System Design Contest)的比赛任务是在Xilinx Ultra96v2平台上实现高速、高准确率且低功耗的飞行器高空目标检测深度学习算法。比赛所用的训练与测试数据集均由大疆公司提供,训练集包含95种目标共93K张图片,测试集包含52K张图片,最终将以检测精度(IoU)高、速度(FPS)快和功耗低为评判准则。

模型设计

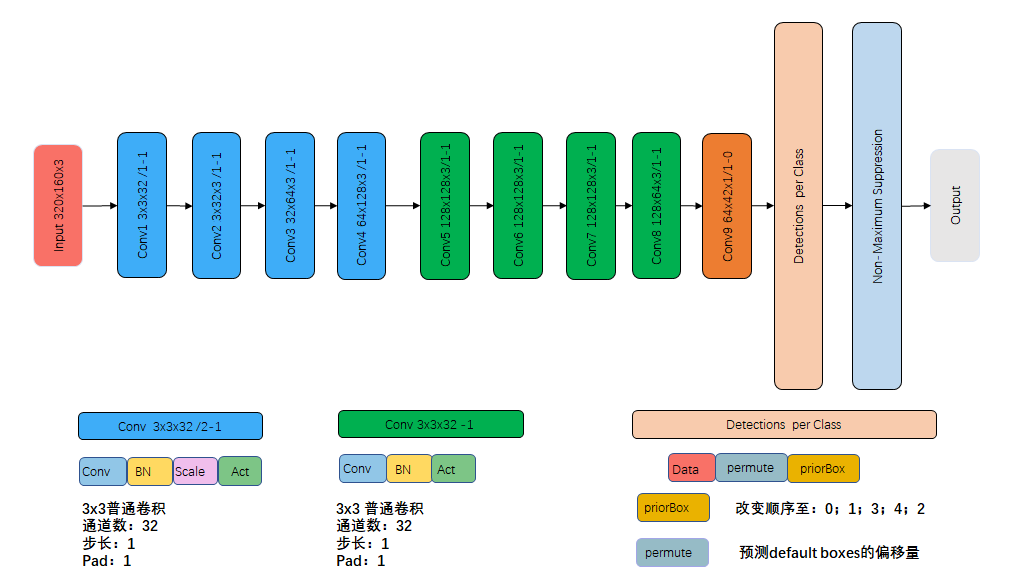

- 轻量化单目标检测网络

- 9层网络,输入图像尺寸为160x320x3

- backbone为类VGG结构; head部分采用YOLO系列结构;boxes select使用confidence最大值选择方法

- 低比特量化

- 权重使用int4,激活值使用uint4,BN参数使用int16

- 权重大小为0.296MB,BN大小为2.9KB

- 精度优化

- 量化感知技术(PACT)、Mosaic数据增强、GIOU损失函数、Adam优化

- 模型训练得到 IoU为0.767

加速器设计

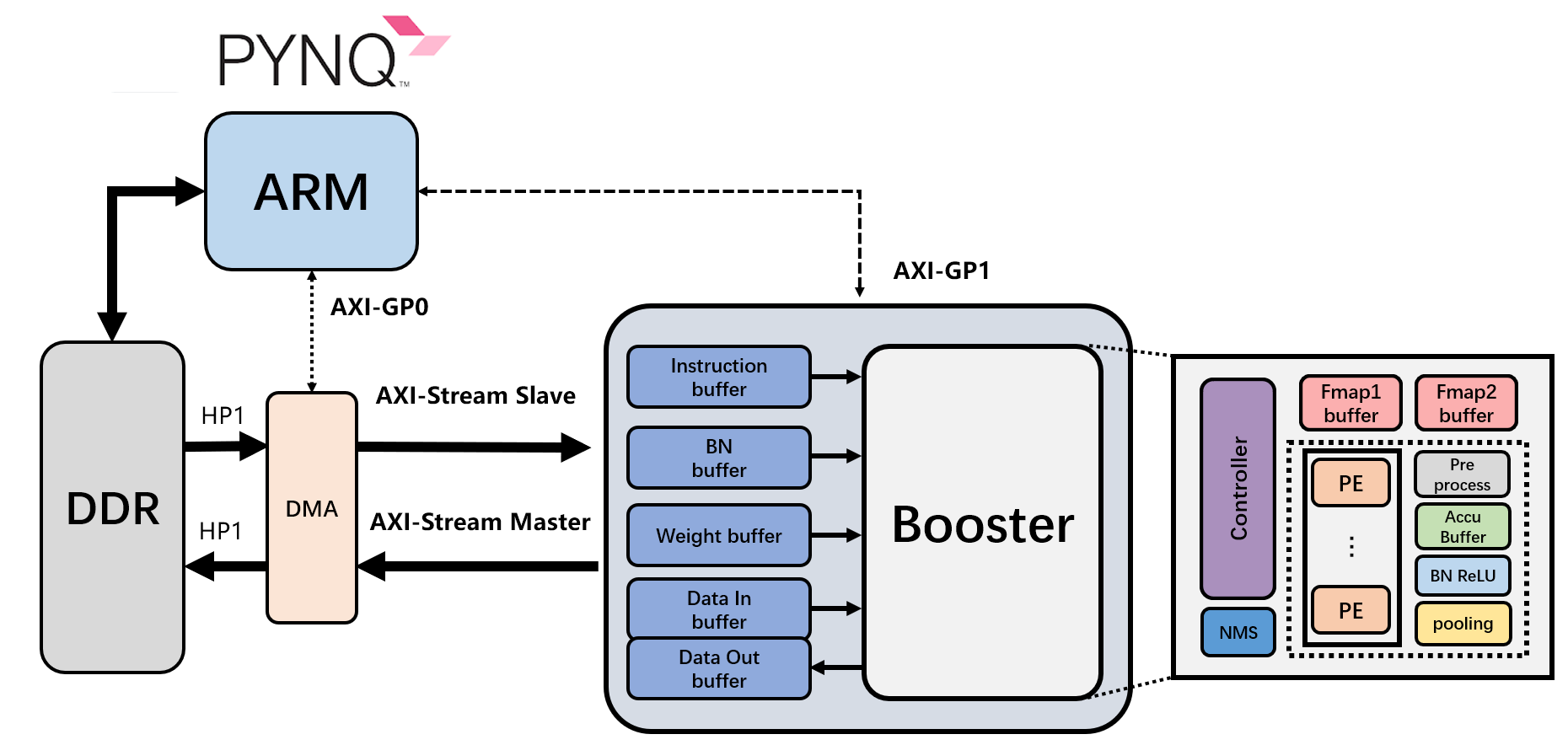

整个系统基于Xilinx Ultra96v2平台搭建,ARM(CPU)端运行装有PYNQ软件框架的Linux系统,CPU通过AXI-GP接口配置加速器和DMA,加速器的数据搬运依靠DMA走AXI-HP接口,使用的是AXI-Stream总线,数据位宽为32bit。加速器系统(Booster System)包含缓存模块、计算模块以及总线接口模块。

缓存模块包含指令缓存、BN参数缓存、权重缓存以及图片的输入和计算结果的输出缓存。

计算模块为加速器Booster的核心模块,主要由控制模块、2块特征图缓存缓存模块、PE模块、预处理模块、累加模块、BN ReLU模块(简称BR模块)、池化模块、NMS后处理模块组成。

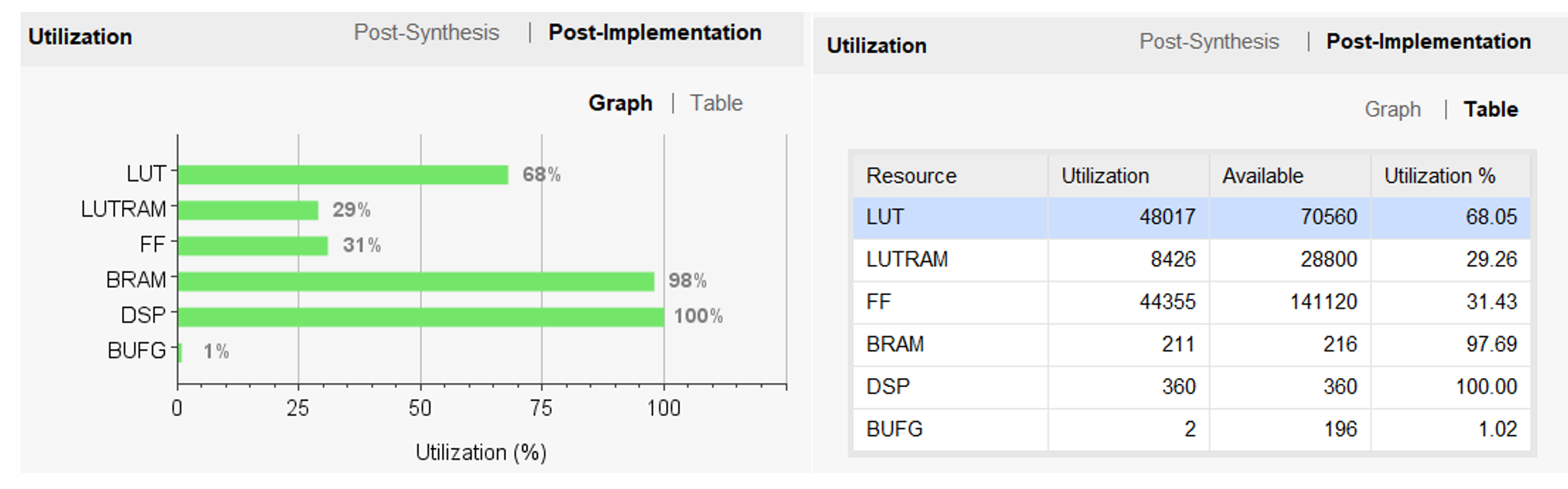

资源消耗

性能测试

| 对比指标 | DAC SDC 2018 1st | DAC SDC 2019 1st | DAC SDC 2020 1st | This work |

|---|---|---|---|---|

| Model | SSD | SkyNet | UltraNet | UltraNet* |

| IOU | 0.624 | 0.716 | 0.656 | 0.680 |

| FPS | 11.96 | 25.05 | 212.73 | 158.00 |

| Power | 4.2 W | 7.26 W | 6.65 W | 4.62 W |

| Energy Eff. | 2.85 Image/W | 3.45 Image/W | 31.99 Image/W | 34.20 Image/W |

- 官方测试集,功耗为ZYNQ芯片功耗,*表示在原有基础上进行修改

- 加速器主频为215MHz,AXI Stream 总线位宽为32bit

- 比赛结果:SEU_Booster (9th/10th*),https://dac-sdc-2021.groups.et.byu.net/doku.php?id=results

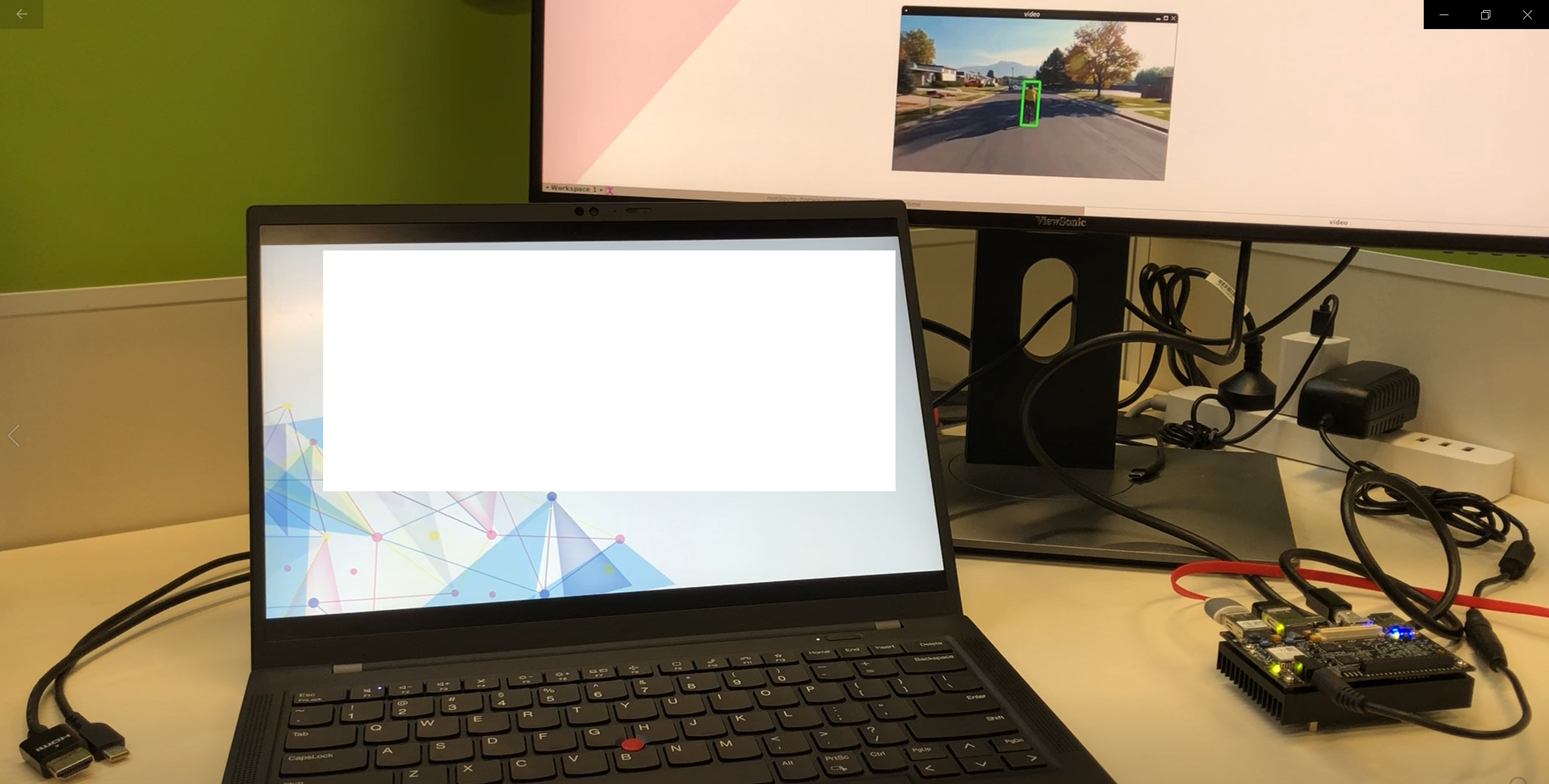

Demo展示